## BIRLA INSTITUTE OF TECHNOLOGY, MESRA, RANCHI (END SEMESTER EXAMINATION)

| CLASS:<br>BRANCH                                                                                                                                                                                                                                                                                                                                                                                                                                  | M.TECH.<br>: ECE                                                                                                                                                                                                                                                                                                                                                     | SEMESTER : II<br>SESSION : SP/2023                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| TIME:                                                                                                                                                                                                                                                                                                                                                                                                                                             | SUBJECT: EC581 ANALOG VLSI DESIGN<br>3 Hours                                                                                                                                                                                                                                                                                                                         | FULL MARKS: 50                                                                                            |

| <ul> <li>INSTRUCTIONS:</li> <li>1. The question paper contains 5 questions each of 10 marks and total 50 marks.</li> <li>2. Attempt all questions.</li> <li>3. The missing data, if any, may be assumed suitably.</li> <li>4. Before attempting the question paper, be sure that you have got the correct question paper.</li> <li>5. Tables/Data hand book/Graph paper etc. to be supplied to the candidates in the examination hall.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                           |

| Q.1(a)<br>Q.1(b)                                                                                                                                                                                                                                                                                                                                                                                                                                  | Determine the voltage gain for a MOS source follower.<br>Find the V <sub>x</sub> and I <sub>x</sub> for the given circuit.<br>And sketch V <sub>x</sub> and I <sub>x</sub> as a function of time.<br>Carrier mobility = $\mu_n$ , Oxide capacitance = C <sub>ox</sub> , Width of the<br>MOSFET = W, Length of the MOSFET = L, Threshold voltage =<br>V <sub>th</sub> | $   I_{X} \qquad [5] \\   I_{X} \qquad V_{X} \qquad [5] \\   I_{1} \qquad I_{2} \qquad C_{1} \qquad [5] $ |

| Q.2(a)                                                                                                                                                                                                                                                                                                                                                                                                                                            | What is the current mirror & what are its applications?<br>What do you mean by Current Sink and Sources?                                                                                                                                                                                                                                                             | [5]                                                                                                       |

Q.2(b) Sketch  $V_X$  and  $V_Y$  as a function of time for the given circuit. Assume the transistors in each circuit are identical.

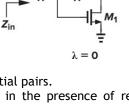

- Q.3(a) Determine the voltage gain of a Common source amplifier for high frequency application. - V<sub>DD</sub> Neglecting other capacitances, calculate the input Q.3(b) impedance of each circuit shown in Figure. (V) 11

- Q.4(a)

- Determine  $(V_{out1} V_{out2})$  as a function of  $(V_{in1} V_{in2})$  for MOS differential pairs. [5] Determine the Common-mode response for MOS differential pairs in the presence of resistor [5] Q.4(b) mismatch.

- Q.5(a) What do you mean by Slew Rate, and CMRR? Draw the building block of Voltage Operational Amplifier?

- Q.5(b) Determine the output voltage of the following circuit.

C<sub>2</sub>

C

[5]

$R_2$ + vo Ξ

VDD

R<sub>1</sub> Y M<sub>1</sub>

> [5] [5]

[5]