## BIRLA INSTITUTE OF TECHNOLOGY, MESRA, RANCHI (END SEMESTER EXAMINATION)

CLASS: BTECH SEMESTER : III

BRANCH: ECE+CS+AIML+EEE SESSION : MO/2023

SUBJECT: EC203 DIGITAL SYSTEM DESIGN

TIME: 3 Hours FULL MARKS: 50

## **INSTRUCTIONS:**

- 1. The question paper contains 5 questions each of 10 marks and total 50 marks.

- 2. Attempt all questions.

- 3. The missing data, if any, may be assumed suitably.

- 4. Before attempting the question paper, be sure that you have got the correct question paper.

- 5. Tables/Data hand book/Graph paper etc. to be supplied to the candidates in the examination hall.

| Q.1(a) | i) Convert the decimal number 165.54 into its hexadecimal equivalent.                                                                                                                                                                           | [2+3]         | <b>CO</b><br>1 | BL<br>1 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|---------|

| Q.1(b) | ii) Define the terms fan-in and fan-out regarding logic gates.  Design a 4 input NAND gate using CMOS transistors and explain the operation.                                                                                                    | [5]           | 1              | 2       |

| Q.2(a) | Minimize the following function using K-map and implement it using NAND gates. $F = \sum (2, 7, 11, 14, 15) + \sum d(0, 3, (10))$                                                                                                               | [5]           | 2              | 1       |

| Q.2(b) | The Excess-3 code is generated by adding 0011 to any BCD input. Design the circuit that coverts a BCD number to the Excess-3 code.                                                                                                              | [5]           | 2              | 2       |

| Q.3(a) | What is the drawback in a parallel adder and how it is overcome in look ahead carry adder? Explain the operation of it with diagram.                                                                                                            | [5]           | 3              | 2       |

| Q.3(b) | <ul> <li>i) Represent a logical diagram of 9's complementor circuit of a BCD input with explanation.</li> <li>ii) Realize the following Boolean function using an appropriate multiplexer F(A, B, C, D) = ∑ (0, 1, 3, 6, 15, 21, 25)</li> </ul> | [2.5+<br>2.5] | 3              | 3       |

| Q.4(a) | What is the drawback in J-K Flip Flop? How is it overcome in Master-Slave J-K Flip-Flop? Explain the operation of it with diagram.                                                                                                              | [5]           | 4              | 2       |

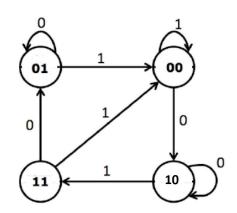

| Q.4(b) | Consider the state diagram shown below, where each state has two bits in the form of $Q_1Q_0$ and the transition is represented by input X. Design the sequential circuit step by step assuming the required Flip Flop is J-K type.             | [5]           | 4              | 3       |

| Q.5(a) | Explain the working of a PAL with a standard logic circuit and diagram. | [5]   | 5 | 2 |

|--------|-------------------------------------------------------------------------|-------|---|---|

| Q.5(b) | i) Describe the working principle of a 4:3 (12 bit) diode matrix ROM.   | [3+2] | 5 | 2 |

ii) What is multivibrator? Discuss their types and applications.