## BIRLA INSTITUTE OF TECHNOLOGY, MESRA, RANCHI (END SEMESTER EXAMINATION MO/2022)

| CLASS: BTECH SEMESTER: V   BRANCH: ECE SUBJECT: EC325 R1DIGITAL SYSTEMS DESIGN WITH FPGAS   TIME: 03 Hours FULL MARKS: 50   INSTRUCTIONS: 1. The question paper contains 5 questions each of 10 marks and total 50 marks.   2. Attempt all questions. 3. The missing data, if any, may be assumed suitably.   4. Tables/Data handbook/Graph paper etc., if applicable, will be supplied to the candidates |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|

| Q.1(a)<br>Q.1(b)                                                                                                                                                                                                                                                                                                                                                                                          | What are some of the most essential goals of the design's standard-cell placement and routing tools?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        | [2]<br>[3]        |

| Q.1(c)                                                                                                                                                                                                                                                                                                                                                                                                    | What are the different FPGA methodologies? Explain the same with neat diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        | [5]               |

| Q.2 (a)<br>Q.2 (b)<br>Q.2(c)                                                                                                                                                                                                                                                                                                                                                                              | ) Write a VHDL Code for 2 to 4 decoder using if else statement?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        | [2]<br>[3]<br>[5] |

| Q.3 (a)<br>Q.3 (b)<br>Q.3(c)                                                                                                                                                                                                                                                                                                                                                                              | Mention a couple of the adder's optimization schemes?<br>What are data paths in digital processor architectures?<br>Design a transmission gate adder circuit and explain its features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | [2]<br>[3]<br>[5] |

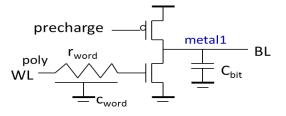

| Q.4(a)<br>Q.4(b)<br>Q.4(c)                                                                                                                                                                                                                                                                                                                                                                                | Outline the several types of memory.<br>Implement and demonstrate the operation of the MOS cell's NOR ROM.<br>Evaluate the propagation delay associated with NOR ROM. Resi<br>0.15ohm, wire capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, and gate capacitance/cell: 0.65 <i>f</i> F and 0.83 <i>f</i> F, | stance/cell: 35ohm and | [2]<br>[3]<br>[5] |

- Q.5(a) Define the term d-frontiers and j-frontiers?

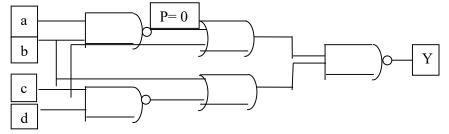

- Q.5(b) Determine the output Y for a stuck-at-fault at P=0.

Q.5(c) Give the different classifications of open circuit faults and briefly explain them.

[5]

[2] [3]

## :::::: 29/11/2022 :::::M