## BIRLA INSTITUTE OF TECHNOLOGY, MESRA, RANCHI (END SEMESTER EXAMINATION)

CLASS: BTECH SEMESTER: V

BRANCH: ECE SESSION: MO/2022

**SUBJECT: EC319 VLSI SYSTEMS**

TIME: 3:00 Hours FULL MARKS: 50

## **INSTRUCTIONS:**

- 1. The question paper contains 5 questions each of 10 marks and total 50 marks.

- 2. Attempt all questions.

- 3. The missing data, if any, may be assumed suitably.

- 4. Before attempting the question paper, be sure that you have got the correct question paper.

- 5. Tables/Data hand book/Graph paper etc. to be supplied to the candidates in the examination hall.

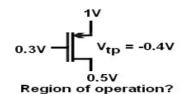

Q1 (a) Find the region of operation of the pMOSFET and nMOSFET shown below. [2] 1 2

## Region of operation?

advantages and disadvantages with proper reasoning.

| Q1<br>Q1 | (b)        | List various secondary effects in a short-channel MOSFETs? Write the expression of dynamic power consumption. Explain each term in it. Write the expression of Power-Delay Product (PDP) and Energy-Delay Product (EDP). Explain each term in them. | [3]<br>[5] | 1 | 1 3    |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|--------|

| Q2       | (a)        | A wire, which is 10 cm long and 1 µm wide, is routed on the polycide, the sheet resistance of which is 4 Ohm-per-square. Compute the total resistance of the wire.                                                                                  | [2]        | 2 | 3      |

| Q2       | (b)        | What is skin effect and skin depth? Express the equation of skin depth mentioning each term in minimum words.                                                                                                                                       | [3]        | 2 | 2      |

| Q2       | (c)        | Explain how a Schmitt trigger circuit can guard against noise-induced false switching when used in an input pad. Substantiate your answer with suitable diagram.                                                                                    | [5]        | 2 | 3      |

| Q3<br>Q3 | (a)<br>(b) | Explain why pseudo nMOS logic circuits are called ratioed circuits?  Diagram the transistor-level circuit diagram of an inverter and implement the same with Verilog HDL using switch-level modeling style.                                         | [2]<br>[3] | 3 | 4<br>4 |

| Q3       | (c)        | Using CMOS logic styles realize the Co (carry out) function, which is given by Co= A.B+Ci.(A+B), and SUM function, which is given by SUM = A.B.Ci + (A+B+Ci), where Ci is the input carry.                                                          | [5]        | 3 | 4      |

| Q4       | (a)        | Schematize transistor-level circuit of CMOS positive-level-sensitive D latch with minimum number MOSFET.                                                                                                                                            | [2]        | 4 | 5      |

| Q4       | (b)        | Schematize transistor-level implementation of SR flip-flop with NAND as well as NOR gate.                                                                                                                                                           | [3]        | 4 | 5      |

| Q4       | (c)        | Schematize multiplexer-based NMOS latch using NMOS-only pass transistors. Explain its                                                                                                                                                               | [5]        | 4 | 5      |

- Q5 (a) A MOSFET is biased at a drain current of 0.5 mA. If  $\mu_n$  Cox = 100  $\mu$ A/V², W/L = 10, and  $\lambda$  [2] 5 5 = 0.1V  $^{-1}$ , estimate its small-signal parameter  $g_m$ .

- Q5 (b) Estimate the small-signal voltage gain of the CS stage shown in Fig. 7.6 if  $I_D = 1$  mA, [3] 5 5  $\mu_n C_{ox} = 100 \ \mu A/V^2$ ,  $V_{TH} = 0.5 \ V$ , and  $\lambda = 0$ . Verify that  $M_1$  operates in saturation.

$$V_{DD} = 1.8 \text{ V}$$

$$R_{D} \ge 1 \text{ k}\Omega$$

$$V_{\text{in}} \sim V_{\text{out}}$$

$$M_{1} \frac{W}{L} = \frac{10}{0.18}$$

Q5 (c) Schematize CS stage with load resistor  $R_D$  and source degeneration resistor  $R_S$ . [5] 5 6 Schematize its small signal model and derive the expression of its voltage gain.

:::::28/11/2022::::M