BIRLA INSTITUTE OF TECHNOLOGY, MESRA, RANCHI

|                                 | BIRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A INSTITUTE OF TECHNOLOGY, MESRA, RANCHI                                                                                                                                                                                                                                                                      |                                                    |                   |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|

| CLASS:<br>BRANCH                | BE<br>I: ECE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                               | SEMESTER : V<br>SESSION : MO/19                    |                   |

| TIME:                           | 3 HOURS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SUBJECT: EC5205 DATA COMMUNICATION                                                                                                                                                                                                                                                                            | FULL MARKS: 60                                     |                   |

| 2. Cand<br>3. The i<br>4. Befor | question paper contains 7<br>idates may attempt any 5<br>nissing data, if any, may b<br>re attempting the questior                                                                                                                                                                                                                                                                                                                                                                                                                                                          | questions each of 12 marks and total 84 marks.<br>questions maximum of 60 marks.<br>be assumed suitably.<br>In paper, be sure that you have got the correct que<br>paper etc. to be supplied to the candidates in the o                                                                                       |                                                    |                   |

| Q.1(a)<br>Q.1(b)<br>Q.1(c)      | Compare the philosophica<br>What is meant by $E_b/N_o$ rat<br>rate on $E_b/N_o$ ratio?<br>If the received signal level                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dulation Noise? How is it caused?<br>l differences between TCP/IP Protocol suite and OSI<br>atio? What is its significance? What is the effect of s<br>for a particular digital system is -151 dBW and the re<br><sup>0</sup> K, what is E <sub>b</sub> /N <sub>o</sub> ratio for a link transmitting at a ra | ignal strength and data<br>ceiver system effective | [2]<br>[4]<br>[6] |

| Q.2(a)<br>Q.2(b)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.2(C)                          | Explain the Delta Modulation (DM) scheme with relevant block diagram and input-output signal [4] waveforms. Why the selection of the step-size is critical in DM scheme?                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.3(a)<br>Q.3(b)<br>Q.3(c)      | What is meant by Hamming distance? What is its significance in Error detection schemes?<br>What is meant by a Null Modem? Why is it required? Justify all connections of Null Modem.<br>For a frame 1011000110110100101 received at the receiver, check whether there is any error in the<br>frame using C.R.C. scheme, if the Generator polynomial $P(x)$ is $x^5 + x^4 + x^3 + x + 1$ . What is the original<br>message, if there is no error? Also mention the number of shift registers and exclusive-OR gates<br>required for the hardware implementation of the same. |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.4(a)<br>Q.4(b)                | and termination, Authentication, Networking and Data transfer phases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.4(c)                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.5(a)                          | What do you understand allocated per channel in D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | by Discrete Multitone (DMT) technology used in A                                                                                                                                                                                                                                                              | DSL? How the bits are                              | [2]               |

| Q.5(b)                          | Compare Synchronous and Asynchronous TDM schemes for N number of sources in terms of bandwidth [-<br>efficiency, number of time slots on the TDM frame, data rate of the multiplexed line, complexity and<br>the buffer requirement to support high traffic load.                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |                                                    |                   |

| Q.5(c)                          | The following 16 sources a<br>of 246 Kbps:<br>Analog 1.5 KHz b<br>Analog 3 KHz bar<br>Analog 4.5 KHz b<br>Analog 6.0 KHz b<br>3 Digital sources<br>4 Digital sources                                                                                                                                                                                                                                                                                                                                                                                                        | are to be multiplexed to obtain a synchronous TDM so<br>andwidth.<br>ndwidth.<br>andwidth.                                                                                                                                                                                                                    | cheme with a data rate                             | [6]               |

• 5 Digital sources of 2700 bps synchronous. Implement the scheme as a block diagram, showing all relevant details.

- Q.6(a) When does a blocking condition occur in a two-stage (TS) digital switch? How this eventuality is [2] resolved in a TST switch?

- Q.6(b) Draw an I/O triangular switch connecting eight stations, and show the connection paths between the [4] stations, if the following stations are communicating each other: 1-7, 2-5, 3-6 and 4-8.

- There are 98 stations to be connected through a Crossbar Matrix switch. What will be the number of Q.6(c) [6] cross points required, if a Single stage switch is used? Compare it with the number of cross points required if a 3-stage Non-blocking (optimized) switch is used. What are the advantages of the second switch over the first switch?

- Q.7(a) What is meant by Congestion in a Packet switched network? How is it caused?

- [2] Q.7(b) The current Routing directory for Node 2 in ARPANET original version is given in Table 1. The delay [4] vectors received at Node 2 from the neighboring nodes are given in Table 2. Update Node 2's Routing directory based on the delay vectors received.

| Destination | Delay | Next Node |

|-------------|-------|-----------|

| 1           | 5     | 4         |

| 2           | 0     | -         |

| 3           | 1     | 3         |

| 4           | 3     | 4         |

| 5           | 6     | 8         |

| 6           | 5     | 8         |

| 7           | 6     | 3         |

| 8           | 2     | 8         |

| 9           | 8     | 8         |

Table-1: Node 2's current Routing directory.

| From Node | From Node | From Node | From Node |

|-----------|-----------|-----------|-----------|

| '1'       | '3'       | '4'       | '8'       |

| 0         | 2         | 4         | 2         |

| 4         | 2         | 3         | 3         |

| 2         | 0         | 2         | 4         |

| 1         | 3         | 0         | 2         |

| 2         | 4         | 2         | 2         |

| 3         | 2         | 1         | 2         |

| 4         | 5         | 2         | 2         |

| 1         | 2         | 1         | 0         |

| 2         | 5         | 1         | 3         |

Table -2: Delay vectors received at Node 2.

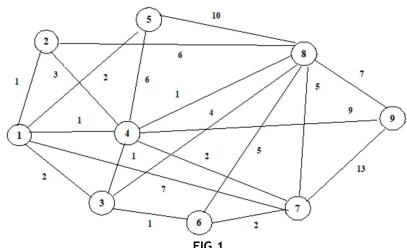

Find out the Least cost paths from **Node 9** to all other nodes for the network shown in Figure 1 using Q.7(c) [6] Bellman-Ford algorithm and form the **Node 9's** Routing table accordingly.

## :::::25/11/2019:::::M